Northeastern engineers develop next-gen chips to tackle quantum computing’s biggest bottlenecks

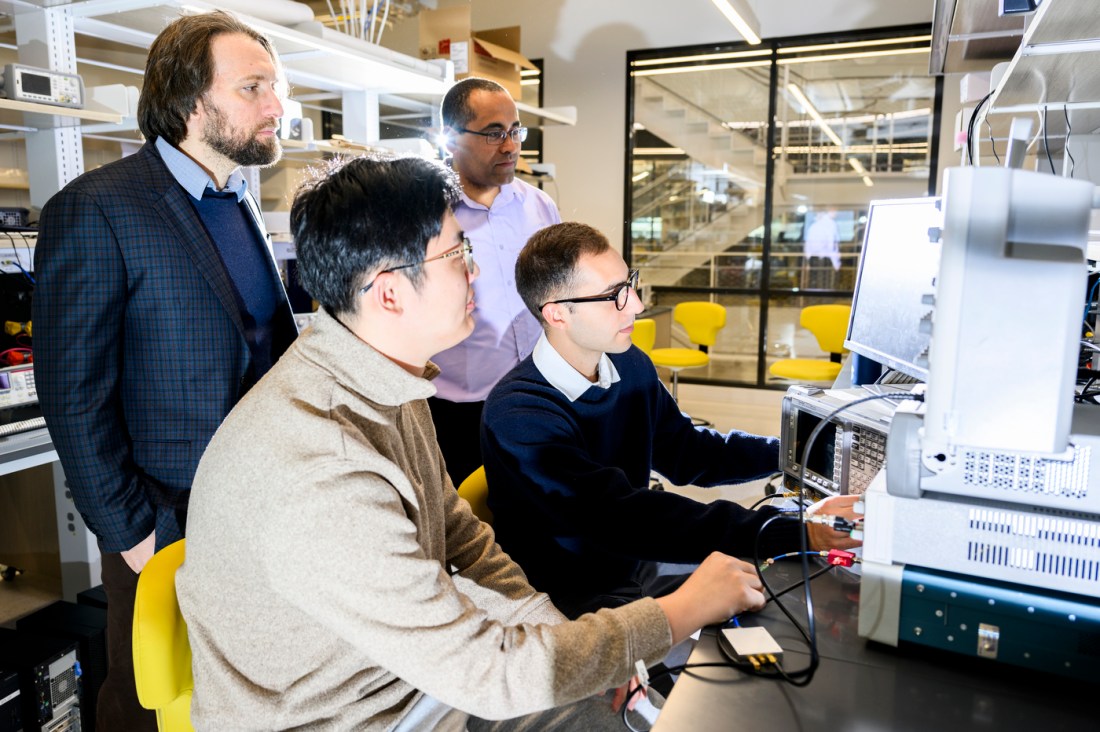

Northeastern professors Cristian Cassella and Marvin Onabajo are developing low-powered chips to improve optimization with help from the Young Scholars Program.

Almost every major industry has them — challenges that cause bottlenecks in day-to-day operations. Think of a scientist working in biotechnology developing drugs, a manager of a cold supply chain operation looking to improve the routes of delivery trucks, or a financial broker trying to maximize their investments.

In quantum computing, these challenges can be framed as quadratic unconstrained binary optimization (QUBO) problems, which are solved using a range of technologies, including machine learning algorithms.

Yet, one of the major computing systems used to handle these tasks — known as oscillator Ising machines (OIMs) — has some major downsides, explains Crisitan Cassella, a Northeastern University professor of electrical and computer engineering.

For one, they aren’t the most efficient in terms of computational power. Second, they aren’t very good at actually solving these problems at a fundamental architectural level, Cassella explains. Third, they aren’t easy to gain access to and can be costly.

Editor’s Picks

Working with Marvin Onabajo, also a Northeastern professor of electrical and computer engineering, Cassella is developing a new class of chips designed specifically to address those problems that are smaller and more energy efficient than OIMs. And they will develop them at Northeastern with the assistance of students in K-12 as part of Northeastern’s Young Scholars Program.

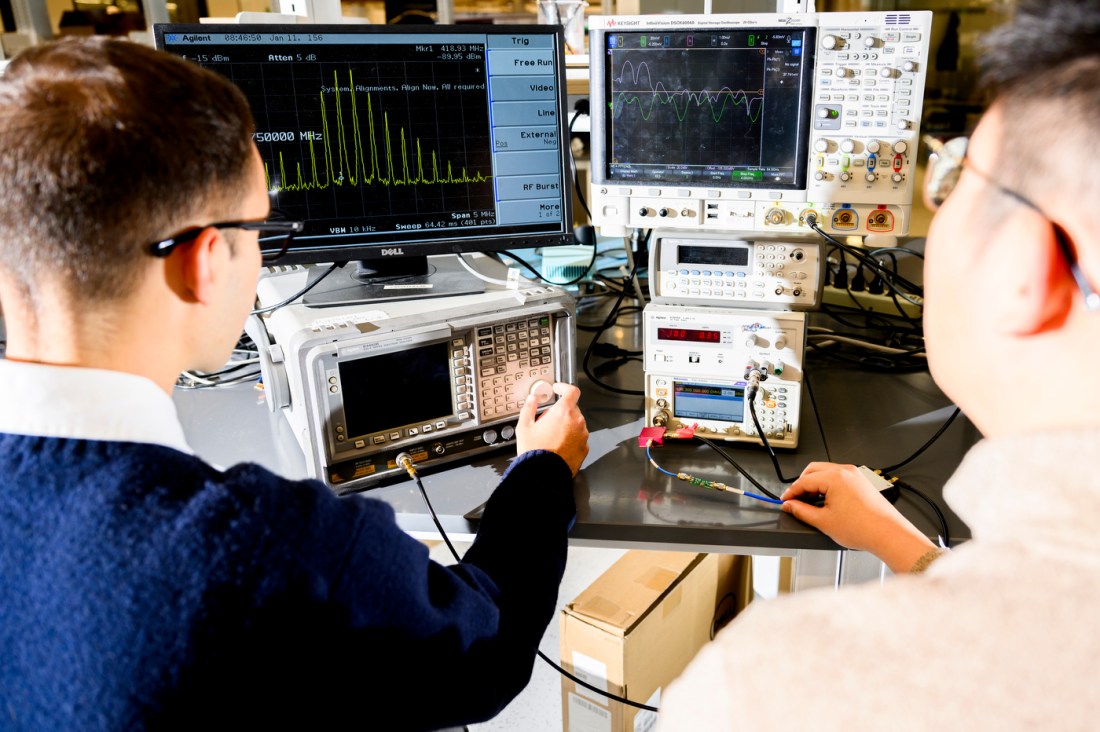

The chips will be manufactured using CMOS technology, explains Onabajo. CMOS stands for complementary metal-oxide-semiconductor.“This will enable the use of standard manufacturing processes for the mass production of computer processors and chips.

“It’s a technology that is used in a widespread manner for digital microprocessors and analog circuits in all your consumer electronic devices,” Onabajo says. “It’s a reliable technology.”

They are projected to consume “10 times less power” than existing systems used to solve QUBO problems, the pair explain. In creating these chips, the researchers hope to “form a new foundation for analog computing” using chips that are smaller, more power-efficient and accessible than what is available today.

“This technology could be an enabler of solving problems that can’t be currently solved with accessible computational technologies,” adds Cassella, noting that these chips will be designed with millions of different variables that no machine today can handle.

“Our platform will be scalable and will use years of development of CMOS technology to provide a system that eventually will be able to solve problems that are much larger than what people can solve today,” he adds.